# CADE-21\_\_\_\_

# The $21^{\mbox{st}}$ Conference on Automated Deduction

# 4th International Verification Workshop VERIFY'07

Editor: Bernhard Beckert

Bremen, Germany, July 15-16, 2007

CADE-21 Organization: Conference Chair: Michael Kohlhase (Jacobs University Bremen) Program Chair: Frank Pfenning (Carnegie Mellon University) Workshop Chair: Christoph Benzmüller (University of Cambridge) Local Organization: Event4 Event Management Π

# Preface

The VERIFY workshop series aims at bringing together people who are interested in the development of safety and security critical systems, in formal methods, in the development of automated theorem proving techniques, and in the development of tool support. Practical experiences gained in realistic verifications are of interest to the automated theorem proving community and new theorem proving techniques should be transferred into practice. The overall objective of the VERIFY workshops is to identify open problems and to discuss possible solutions under the theme "What are the verification problems? What are the deduction techniques?".

This volume contains the research papers presented at the 4th International Verification Workshop (VERIFY'07) held July 15–16, 2007 in Bremen, Germany. This workshop was the 4th in a series of international meetings since 2002. It was affiliated with the 21st Conference on Automated Deduction (CADE-21).

Each paper submitted to the workshop was reviewed by three referees, and an intensive discussion on the borderline papers was held during the online meeting of the Program Committee. 13 research papers were accepted based on originality, technical soundness, presentation, and relevance. I wish to sincerely thank all the authors who submitted their work for consideration. And I would like to thank the Program Committee members and other referees for their great effort and professional work in the review and selection process. Their names are listed on the following pages.

In addition to the contributed papers, the program included three excellent keynote talks. I am grateful to Prof. Cesare Tinelli (The University of Iowa, USA), Prof. Tobias Nipkow (TU München, Germany), and Prof. Aaron Stump (Washington University in St. Louis, USA) for accepting the invitation to address the workshop.

July 2007

Bernhard Beckert

IV

# Program Chair and Organiser

Bernhard Beckert University of Koblenz-Landau, Germany

# **Program Committee**

| Serge Autexier<br>Yves Bertot<br>Bruno Dutertre<br>Reiner Hähnle<br>Dieter Hutter<br>Andrew Ireland<br>Deepak Kapur<br>Joost-Pieter Katoen<br>Joseph Kiniry<br>Heiko Mantel<br>Fabio Massacci<br>Stephan Merz<br>Till Mossakowski<br>Lawrence C. Paulson<br>Wolfgang Reif<br>Julian Richardson<br>Luca Viganò | DFKI & University Saarbrücken, Germany<br>INRIA Sophia Antipolis, France<br>SRI International, USA<br>Chalmers University, Gothenburg, Sweden<br>DFKI Saarbrücken, Germany<br>Heriot-Watt University, Edinburgh, UK<br>University of New Mexico, USA<br>RWTH Aachen, Germany<br>University Dublin, Ireland<br>RWTH Aachen, Germany<br>University of Trento, Italy<br>INRIA Lorraine, France<br>University of Bremen, Germany<br>University of Bremen, Germany<br>University of Cambridge, UK<br>University of Augsburg, Germany<br>Powerset Inc., USA<br>University of Verona, Italy |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Christoph Walther                                                                                                                                                                                                                                                                                             | TU Darmstadt, Germany                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# Steering Committee

| Serge Autexier | DFKI & University Saarbrücken, Germany |

|----------------|----------------------------------------|

| Heiko Mantel   | RWTH Aachen, Germany                   |

## **Additional Referees**

Dominik Haneberg Holger Grandy Kurt Stenzel VI

# Table of Contents

# Invited Talks

| Reflecting Linear Arithmetic: From Dense Linear Orders to Presburger<br>Arithmetic                                                                 | 1   |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Lightweight Verification with Dependent Types                                                                                                      | 2   |

| Trends and Challenges in Satisfiability Modulo Theories<br>Cesare Tinelli                                                                          | 3   |

| Research Papers                                                                                                                                    |     |

| Formal Device and Programming Model for a Serial Interface<br>Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev,<br>Sergey Tverdyshev | 4   |

| A Mechanization of Phylogenetic Trees                                                                                                              | 21  |

| Combinations of Theories and the Bernays-Schönfinkel-Ramsey Class<br>Pascal Fontaine                                                               | 37  |

| ALICE: An Advanced Logic for Interactive Component Engineering<br>Borislav Gajanovic, Bernhard Rumpe                                               | 55  |

| A History-based Verification of Distributed Applications<br>Bruno Langenstein, Andreas Nonnengart, Georg Rock, Werner Stephan                      | 70  |

| Symbolic Fault Injection<br>Daniel Larsson, Reiner Hähnle                                                                                          | 85  |

| A Termination Checker for Isabelle Hoare logic<br>Jia Meng, Lawrence C. Paulson, Gerwin Klein                                                      | 104 |

| The Heterogeneous Tool Set<br>Till Mossakowski, Christian Maeder, Klaus Lüttich                                                                    | 119 |

| Fully Verified JAVA CARD API Reference Implementation                                                                                              | 136 |

| Automated Formal Verification of PLC Programs Written in IL<br>Olivera Pavlovic, Ralf Pinger, Maik Kollmann                                        | 152 |

| Combining Deduction and Algebraic Constraints for Hybrid System<br>Analysis                   | 164 |

|-----------------------------------------------------------------------------------------------|-----|

| A Sequent Calculus for Integer Arithmetic with Counterexample<br>Generation<br>Philipp Rümmer | 179 |

| Inferring Invariants by Symbolic Execution<br>Peter H. Schmitt, Benjamin Weiß                 | 195 |

| Author Index                                                                                  | 211 |

# VIII

# Reflecting Linear Arithmetic: From Dense Linear Orders to Presburger Arithmetic

Tobias Nipkow

Institut für Informatik, Technische Universität München http://www.in.tum.de/~nipkow

#### Abstract

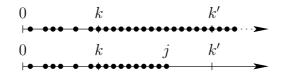

This talk presents reflected quantifier elimination procedures for both integer and real linear arithmetic. Reflection means that the algorithms are expressed as recursive functions on recursive data types inside some logic (in our case HOL), are verified in that logic, and can then be applied to the logic itself. After a brief overview of reflection we will discuss a number of quantifier elimination algorithms for the following theories:

- Dense linear orders without endpoints. We formalize the standard DNF-based algorithm from the literature.

- Linear real arithmetic. We present both a DNF-based algorithm extending the case of dense linear orders and an optimized version of the algorithm by Ferrante and Rackoff [3].

- Presburger arithmetic. Again we show both a naive DNF-based algorithm and the DNF-avoiding one by Cooper [2].

We concentrate on the algorithms and their formulation in Isabelle/HOL, using the concept of *locales* to allow modular definitions and verification. Some of the details can be found in joint work with Amine Chaib [1].

# References

- 1. A. Chaieb and T. Nipkow. Proof synthesis and reflection for linear arithmetic. Technical report, Institut für Informatik, Technische Universität München, 2006. Submitted for publication.

- D. Cooper. Theorem proving in arithmetic without multiplication. In B. Meltzer and D. Michie, editors, *Machine Intelligence*, volume 7, pages 91–100. Edinburgh University Press, 1972.

- 3. J. Ferrante and C. Rackoff. A decision procedure for the first order theory of real addition with order. SIAM J. Computing, 4:69–76, 1975.

# Lightweight Verification with Dependent Types

Aaron Stump

Computer Science and Engineering Dept. Washington University in St. Louis

#### Abstract

Dependent types, studied for many years in Logic, have recently been gaining attention in Functional Programming Languages for expressing rich properties as types. A simple example is a type  $\langle list \ A \ n \rangle$ , for lists of length n holding objects of type A. A more complex example is  $\langle trm \ G \ T \rangle$ , for terms in some object language which have object-language type T in context G. Dependently typed programming languages seek to support static verification of code manipulating such data types, by statically enforcing the constraints the data types impose. The verification is lightweight in the sense that the aim is typically to verify programs.

This talk will explore dependently typed programming in the context of Guru, a new dependently typed programming language under development at Washington University in St. Louis. Guru lifts the restriction to terminating programs which is commonly required by dependently typed programming languages (such as Coq, Epigram, and ATS, to name just a few). This is done by the novel technical feature of strictly separating program terms from proofs, and types from formulas, thus going counter to the commonly used Curry-Howard isomorphism. We will consider dependently typed programming in Guru via several examples: tree operations which are statically verified to preserve the binary search tree property, and compilation of simply typed object programs which is statically verified to preserve the programs' object-language type.

# Trends and Challenges in Satisfiability Modulo Theories

Cesare Tinelli\*

Department of Computer Science The University of Iowa tinelli@cs.uiowa.edu

#### Abstract

Satisfiability Modulo Theories (SMT) is concerned with the problem of determining the satisfiability of first-order formulas with respect to a given logical theory T. A distinguishing feature of SMT is the use of inference methods tailored to the particular theory T. By being theory-specific and restricting their language to certain classes of formulas (such as, typically but not exclusively, ground formulas), such methods can be implemented into solvers that are more efficient in practice than general-purpose theorem provers. SMT techniques have been traditionally developed to support deductive software verification, but they have also applications in model checking, certifying compilers, automated test generation, and other formal methods.

This talk gives an overview of SMT and its applications, and highlights some long-standing challenges for a wider applications of SMT techniques within formal methods, as well as some fresh challenges introduced by new potential uses. A major challenge is providing adequate model generation features for disproving verification conditions.

<sup>\*</sup> The author's research described in this talk was made possible with the partial support of grants #0237422 and #0551646 from the National Science Foundation and a grant from Intel Corporation.

# Formal Device and Programming Model for a Serial Interface

Eyad Alkassar<sup>1,\*</sup>, Mark Hillebrand<sup>2,\*</sup>, Steffen Knapp<sup>1,\*</sup>, Rostislav Rusev<sup>1,\*</sup>, and Sergey Tverdyshev<sup>1,\*</sup>

<sup>1</sup> Saarland University, Dept. of Computer Science, 66123 Saarbrücken, Germany {eyad, sknapp, rusev, deru}@wjpserver.cs.uni-sb.de

<sup>2</sup> German Research Center for Artificial Intelligence (DFKI GmbH), Stuhlsatzenhausweg 3, 66123 Saarbrücken, Germany mah@dfki.de

**Abstract.** The verification of device drivers is essential for the pervasive verification of an operating system. To show the correctness of device drivers, devices have to be formally modeled. In this paper we present the formal model of the serial interface controller UART 16550A. By combining the device model with a formal model of a processor instruction set architecture we obtain an assembler-level programming model for a serial interface. As a programming and verification example we present a simple UART driver implemented in assembler and prove its correctness. All models presented in this paper have been formally specified in the Isabelle/HOL theorem prover.

# **1** Introduction

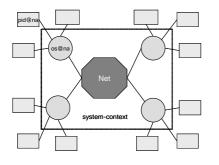

The Verisoft project [1] aims at the pervasive modeling, implementation, and verification of complete computer systems, from gate-level hardware to applications running on top of an operating system. The considered systems employ various devices, e.g., a hard disk controller for persistent storage, a time-triggered bus controller for communication in a distributed system, and a serial interface for user interaction via a terminal. The drivers controlling these devices are part of the operating system and proving their correctness is critical to proving the correctness of the system as a whole.

Here we consider a system which the user may control with a terminal connected via a serial interface. To prove the functional correctness of the serial interface device driver it is not sufficient to argue only about the driver code; the serial interface itself and its interaction with the processor have to be formally modeled, too. In this paper we present for the first time a formal model of a serial interface and its programming model at the assembler language level. Furthermore, as an informal example, we present a serial interface driver and sketch its correctness proof with respect to our models.

The remainder of this paper is structured as follows. In Sect. 2 we discuss previous and related work. In Sect. 3 we sketch the instruction set architecture of the VAMP

<sup>\*</sup> Work of the first author was supported by the German Research Foundation (DFG) within the program 'Performance Guarantees for Computer Systems'. Work of the third author was supported by the International Max Planck Research School for Computer Science (IMPRS). Work of all but the fourth author was supported by the German Federal Ministry of Education and Research (BMBF) in the Verisoft project under grant 01 IS C38.

processor [2, 3] and show how memory-mapped devices can be integrated into this architecture. In Sect. 4 we present the formal model of a UART 16550A controller and formalized environmental and software conditions. To informally demonstrate the utility of the framework, in Sect. 5 we present a simple driver written in assembler, which writes several words to the serial interface. We sketch its correctness proof.

## **2** Previous and Related Work

For the pervasive verification of computer systems, as done in the Verisoft project, devices must be modeled at different system layers. Some results of Verisoft's completed or ongoing work in the context of devices and their drivers have already been published. One subproject of Verisoft deals with the verification of a FlexRay-like shared serial bus interface to be used in distributed automotive systems. To verify such a system we need to argue formally about low-level clock synchronization [4], gate-level implementation, and driver real-time properties of the FlexRay interface. All these arguments will finally be combined into one formal pervasive correctness proof. A paper-and-pencil style description of this ongoing effort can be found in Knapp and Paul [5].

In another Verisoft subproject the formal pervasive verification of a general-purpose computer system is attempted. In this context, Hillebrand *et al.* [6] presented paperand-pencil formalizations of a system with devices for the gate and the assembler level. For a hard disk as a specific device, correctness arguments justifying these models and a correctness proof for a disk driver were given on paper. Here we *formalize* large portions of [6] for a communication device.

So far almost all other device related verification approaches have either aimed at the correctness of a gate-level implementation or at showing safety properties of drivers.

In approaches of the former kind, simulation- and test based techniques are used to check for errors in the hardware designs. In particular, [7–10] deal with UARTs in that manner. Berry *et al.* [8] specified a UART model in a synchronous language and proved a set of safety properties regarding FIFO queues. From that model a hardware description can be generated (either in RTL or software simulation) and run on a FPGA.

In approaches of the latter kind the driver code is usually shown to guarantee certain API constraints of the operating system and hence cannot cause the system to crash. For example, the SLAM project [11] provides tools for the validation of safety properties of drivers written in C. Lately, the success of the SLAM project led to the deployment of the Static Driver Verifier (SDV) as part of the Windows Driver Foundation [12]. SDV automatically checks a set of 65 safety rules concerning Windows Driver API for given C driver programs. Hallgren *et al.* [13] modeled device interfaces for a simple operating system implemented in Haskell. Three basic memory-mapped I/O primitives were specified: read, write, and a test for valid region.

Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev, Sergey Tverdyshev

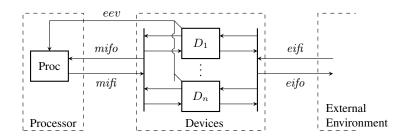

Fig. 1. Overview: A System with Processor and Devices

However, the only correctness property being stated is the disjointness of the device address spaces.

In contrary to all mentioned approaches, we aim at the formalization and *functional* verification a (UART) driver interacting with a device. Thus, it is not sufficient to argue about the device or the programming model alone. Similar in scope is the 'mini challenge' proposed by Holzmann [14], which deals with the formal verification of a file system for a Flash device. Apparently, formalizing the device and its interaction with the driver is also part of the challenge. However, no details have yet been published.

#### **3 Processor and Devices**

6

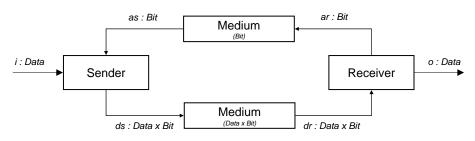

In this section we define the instruction set architecture (ISA) of a processor with memory-mapped devices as depicted in Fig. 1.

Compared to regular ISA definitions we have the following differences: in addition to the processor state, the state space of the combined architecture also includes devices states. Processor and devices may interact (i) by the processor issuing memory operations to special memory regions (device addresses) and (ii) by the device causing interrupts. Additionally, devices can make computational steps on their own when interacting with an external environment (e.g., a network). Therefore we model the computation of ISA with devices as an interleaved computation.

Note that at the hardware level processor and devices run in parallel and not interleaved. This requires some non-trivial extensions of the formal hardware correctness proof, which we will report on elsewhere.

#### 3.1 Processor

A processor configuration  $c_{\rm P}$  is a tuple consisting of (i) two program counters  $c_{\rm P}.pc$ and  $c_{\rm P}.dpc$  implementing delayed branching, (ii) general purpose, floating point, and special purpose register files  $c_{\rm P}.gpr$ ,  $c_{\rm P}.fpr$ ,  $c_{\rm P}.spr$ , and (iii) a byte addressable memory  $c_{\rm P}.m$ . Devices are mapped into the processor memory. Thus by simple read and write operations the processor can access them. In addition devices can signal an interrupt to the processor via an external event signal (cf. Fig. 1).

Let DA denote the set of memory addresses mapping to devices, which are disjoint from regular physical memory addresses. The processor indicates an access to an address in DA via the memory interface input *mifi* and receives the device's response on the memory interface output *mifo*; this naming convention is from the point of view of the devices.

Formally, let the predicates  $lw(c_{\rm P})$  and  $sw(c_{\rm P})$  indicate load and store word instructions and let  $ea(c_{\rm P})$  and  $RD(c_{\rm P})$  denote the address and affected processor register for such operations (see Müller and Paul [15] for full definitions).

The memory interface input has the following four components: (i) the read flag  $mifi.rd = lw(c_P) \land ea(c_P) \in DA$  is set for a load from a device address, (ii) the write flag  $mifi.wr = sw(c_P) \land ea(c_P) \in DA$  is set for a store to a device address, (iii) the address  $mifi.a = ea(c_P)$  is set to the effective address, with ea[14 : 12] specifying the accessed device and ea[11 : 2] specifying the accessed device port (we support up to eight devices with up to 1024 ports of width 32 bits), and finally (iv) the data input  $mifi.din = c_P.gpr[RD(c_P)]$  is set to the store operand.

The memory interface output  $mifo \in \{0, 1\}^{32}$  contains the device's response for a load operation on a device.

The processor model is defined by the output function  $\omega_{\rm P}$  and the next state function  $\delta_{\rm P}$ . The former takes a processor state  $c_{\rm P}$  and computes a memory interface input *mifi* to the device as defined above. The latter takes a processor state  $c_{\rm P}$ , a device output *mifo*, and an external event (interrupt) vector *eev* (where *eev*[*i*] is set iff device  $D_i$  indicates an interrupt). It returns the next state of the processor  $c'_{\rm P}$ .

#### 3.2 Devices

The configurations of all devices are combined in a mapping  $c_D$  from an index  $D_i$  to the corresponding device configuration.

Our device model is sequential in the sense that a device may progress either due to a processor access or an input from the external environment. To distinguish both cases we extend the set of device indices by the processor index P and denote this set by PD.

The device transition function  $\delta_{\rm D}$  specifies the interaction of the devices with the processor and the external environment. It takes a processor-device index  $idx \in PD$ , an input from the external environment  $eif_i$ , an input from the processor  $mif_i$ , and a combined device configuration  $c_{\rm D}$ . It returns a new device configuration  $c'_{\rm D}$ , an output to the processor  $mif_o$ , and an external output  $eif_o$ .

Depending on the input index idx and the memory input  $mif_i$ , the transition function  $\delta_D$  is defined according to the following three cases:

8 Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev, Sergey Tverdyshev

- If  $idx \neq P$ , a step of the device idx is triggered by the external input *eifi*. In this case  $\delta_D$  ignores the given *mifi*.

- If *idx* = P ∧ (*mifi.wr* ∨ *mifi.rd*), a device step is triggered by a processor device access. In this case δ<sub>D</sub> ignores the given *eifi* and produces an arbitrary *eifo*. The device being accessed as well as the access-type is specified by the given *mifi*.

- Otherwise the processor does not access any device. In this case,  $\delta_D$  does nothing.

The device output function  $\omega_D$  computes the external event vector *eev* for the processor based on the current device configurations.

#### 3.3 Combined System

By combining the processor and device models we obtain a model for the overall system with devices as depicted in Fig. 1. This model allows interaction with an external environment via *eifi* and *eifo* whereas the communication between processor and devices is not visible from the outside anymore.

A configuration  $c_{PD}$  of the combined model consists of a processor configuration  $c_{PD}.c_{P}$  and device configurations  $c_{PD}.c_{D}$ .

Similarly to the previous models, we define a transition function  $\delta_{PD}$  and an output function  $\omega_{PD}$ . Both functions take the same three inputs: a processor-device index *idx*, a configuration  $c_{PD}$ , and an external input *eifi*.

We introduce some more notation for the transition and the output function. Let  $mifi = \omega_{\rm P}(c_{\rm PD}.c_{\rm P})$  be the memory interface input from the processor to the devices. Let  $(c'_{\rm PD}.c_{\rm D}, mifo, eifo) = \delta_{\rm D}(idx, c_{\rm PD}.c_{\rm D}, eifi, mifi)$  denote the updated device configuration, the memory output to the processor, and the external output. Let  $eev = \omega_{\rm D}(c'_{\rm PD}.c_{\rm D})$  denote the external event vector, which is computed based on the updated device configuration. Finally, if idx = P then  $c'_{\rm PD}.c_{\rm P}$  denotes the updated processor configuration, i.e.,  $c'_{\rm PD}.c_{\rm P} = \delta_{\rm P}(c_{\rm PD}.c_{\rm P}, eev, mifo)$ . Otherwise  $c'_{\rm PD}.c_{\rm P}$  denotes the unchanged processor configuration, i.e.,  $c'_{\rm PD}.c_{\rm P} = c_{\rm PD}.c_{\rm P}$ .

The transition function  $\delta_{\text{PD}}$  returns the new configuration,  $\delta_{\text{PD}}(idx, eif_i, c_{\text{PD}}) = c'_{\text{PD}}$ . The output function  $\omega_{\text{PD}}$  simply returns the output to the external environment,  $\omega_{\text{PD}}(idx, c_{\text{PD}}, eif_i) = eif_o$ .

#### 3.4 Model Run

A model run is computed by the function  $run_{PD}$ , which executes a number of steps in the combined model. It takes as inputs an initial configuration  $c_{PD}^0$ , a number of steps *i*, an external input sequence  $eifiseq \in \mathbb{N} \rightarrow eifi$ , and a computational sequence  $seq_{PD} \in \mathbb{N} \rightarrow PD$ , which designates the interleaving of the processor and device steps. It returns an updated configuration  $c'_{PD}$  and an external output sequence  $eifoseq \in \mathbb{N} \rightarrow eifo$ .

The run function  $run_{PD}$  is defined by recursive application of  $\delta_{PD}$ . For the base case, i.e., i = 0, we set  $run_{PD}(0, seq_{PD}, eifiseq, c_{PD}^0) = (c_{PD}^0, \langle \rangle)$ .

For i + 1, let  $(c_{\text{PD}}, eifoseq) = run_{\text{PD}}(i, seq_{\text{PD}}, eifiseq, c_{\text{PD}}^0)$  denote configurations and outputs after executing i steps. To execute the (i + 1)-th step, we apply the transition and output function of the combined model one more time. Let  $c'_{\text{PD}} = \delta_{\text{PD}}(seq_{\text{PD}}(i), eifiseq(i), c_{\text{PD}})$  and  $eifo = \omega_{\text{PD}}(seq_{\text{PD}}(i), eifiseq(i), c_{\text{PD}})$ . We define  $run_{\text{PD}}(i + 1, seq_{\text{PD}}, eifiseq, c_{\text{PD}}^0) = (c'_{\text{PD}}, eifoseq \circ (eifo, seq_{\text{PD}}(i)))$ .

## 4 Serial Interface (UART 16550A)

The *universal asynchronous receiver / transmitter* (UART) is a chip for communication over a serial interface. In the following we will simply speak of a serial interface.

A serial interface provides a computing device with the capability to send data via a few copper wires to another serial interface. This facility is used for non-network communication, e.g., with terminals, modems, and other computers.

In this section we describe the driver programmer's model of the serial interface chip UART 16550A [16]. Briefly summarized, the processor can send or receive data byte-wise. In case of a send this byte is stored in a FIFO queue, called the transmitter buffer, and later on sent to the external environment. A receiver buffer stores all incoming bytes from the environment. Reads from the programmer are served in FIFO manner, too. The UART provides the programmer with two methods to access status information for both buffers: either by interrupts or by polling special ports.

The transmitter and receiver queue are bounded in size (16 bytes); thus they may overrun. The receiver queue may overrun if the speed of incoming data from the environment exceeds the speed at which the processor can handle it. The transmitter queue may overrun if the processor writes data into the transmitter buffer faster than the serial interface can send out the data to the environment. Another error related to the queue size occurs when an empty receiver queue is read.

Our model handles the three error cases as follows: (i) overruns in the receiver queue are treated according to the UART specification, i.e., new incoming bytes are dropped, (ii) writing to a full transmitter queue and reading the empty receiver buffer are not allowed in our model, they are excluded through explicit software conditions.

Discharging these software conditions for a particular driver is tricky, and obviously it would be desirable to find easier accessible programming rules, e.g., write only if the transmitter buffer signals that it is empty. Proving that a concrete system will never let the receiver queue overrun, is even harder. A programmer would typically rely on run-time estimations, which ensure that the environment does not send data faster than the driver code can handle (when running on a certain machine). However, our model does not provide any real-time bounds on computations, and hence proving correctness of a concrete system would either require further assumptions over the environment (e.g., as part of a communication protocol between two serial interfaces) or correctness criteria which tolerate overruns.

For brevity, in this paper we do not go into detail regarding the *memory control* register and the *memory status register*. These registers are used to address additional

10 Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev, Sergey Tverdyshev

wires connected to some external modem and to configure hardware flow control. The remainder of this section is structured as follows. In Sect. 4.1 the configuration and the ports of the serial interface is detailed. The transition function  $\delta_u$  of the serial interface is split into two logical parts: a processor- and an environment sided transition function. The first part is specified in Sect. 4.2, the second in Sect. 4.3. Finally in Sect. 4.4 all required software and environment restrictions are stated and different ways of discharging them are discussed.

#### 4.1 Configuration

In the definition of the UART we use FIFO queues  $C_T$  of maximum size 16 for types T. For example, we use queues of type  $C_{\mathbb{R}^8}$  to send and receive data.

We model these queues by cyclic buffers with head and tail pointers hd and tl. The buffer content ct maps indices to elements of type T. The number of queue entries is denoted as len.

Queues with len = 0 and len = 16 are called empty and full. The head element of a queue is accessed by head(b) = b.ct(b.hd). Queues are manipulated by the operations *push* and *pop*. The function *push* adds a new byte to the queue at the tail pointer. It is only defined for non-full queues. We set push(bdin, b) = b' where  $b'.ct[b.tl] = bdin, b'.tl = (b.tl + 1) \mod 16$  and b'.len = b.len + 1. The function *pop* deletes the element pointed to by the head pointer. It is only defined for non-empty queues. We set pop(b) = b' where  $b'.hd = (b.hd + 1) \mod 16$  and b'.len = b.len - 1. A configuration of a serial interface  $c_u$  is a record with the following components:

1. The transmitter holding buffer  $thb \in C_{\mathbb{B}^8}$  is a FIFO byte queue of size 16. Input bytes from the external environment are stored in chronological order. The transmitter holding buffer can be read byte-wise by the programmer.

2. The *receiver buffer*  $rb \in C_{\mathbb{B}^8}$  is a FIFO byte queue of size 16. It can be written byte-wise by the programmer.

3. Interrupt driven mode configuration. The serial interface generates four types of interrupts (mapped to a single interrupt line). For each type two kinds of flags are maintained in the configuration: one indicating whether the interrupt type is enabled or disabled and the other indicating whether a corresponding interrupt is still pending.

- The received data available interrupt is generated, when the number of bytes in the receive buffer exceeds its interrupt trigger level. This level is computed as  $itl(x) = 7x[1] + 3x[0] \cdot (x[1] + 1) + 1 \in \{1, 4, 8, 14\}$  for  $x = c_u.rbitl \in \mathbb{B}^2$ . The component  $c_u.erdai \in \mathbb{B}$  indicates if the interrupt is enabled or not, while  $c_u.rdai \in \mathbb{B}$  indicates if the interrupt is currently pending.

- The transmitter holding buffer empty interrupt is generated if the transmitter buffer is empty. The component  $c_u.ethrei \in \mathbb{B}$  indicates if the interrupt is enabled or not, while  $c_u.threi \in \mathbb{B}$  indicates if it is currently pending.

- The *receiver line status interrupt* is generated if certain transmission errors occur. These are *overrun*, *parity*, *framing*, and *breaking* errors. The components  $c_{u.}oe$

specifies if an overrun in one of the two queues occurred. The *parity*, *framing*, and *breaking* errors are linked to particular bytes in the receiver queue. Their occurrence is saved in the 3-bit FIFO queue  $c_u.trerr \in C_{\mathbb{B}^3}$ . For example, 110 encodes a parity and a framing error in the corresponding byte of the receiver queue.

- The *timeout interrupt* is generated if for a certain period of time no data was received or read from the receiver queue. The UART sets this timeout to the time needed to receive four bytes. This interrupt type can be used by the programmer to ensure that no data is forgotten in the receive queue after the input stream ended. The component  $c_u.toi \in \mathbb{B}$  indicates if the interrupt is currently pending. This interrupt is enabled iff the received data available interrupt is.

4. Polling mode configuration. The serial interface can also be operated in polling mode, in which the driver can check the status of the buffers by reading special ports. These ports map to three boolean configuration components: the data ready flag  $c_u.dr \in \mathbb{B}$ , the empty transmitter holding buffer flag  $c_u.ethb$ , and the empty data holding registers flag  $c_u.edhr$ .

It is possible to mix interrupt and polling modes, e.g., the programmer could be informed about incoming data by an interrupt and then read the receiver buffer as long as it is non-empty.

5. Word length configuration. The following components can be set by the programmer, but do not affect the modeled behavior of our device. Nevertheless we need to model them: when connecting two serial interfaces the word length must be configured equally on both sides.

The serial interface uses a timer with a 115.2 kHz frequency; the *baud rate* is computed as  $115200/c_u.div$ . Due to port overloading the programmer has to set a so-called *Divisor Latch Access Bit*  $c_u.dlab \in \mathbb{B}$  before accessing the  $c_u.div$  field.

The low-level encoding of the transmitted data (including error protection) is configured via the *word length*  $c_u.wl \in \mathbb{B}^2$ , the stop bit length  $c_u.sbl \in \mathbb{B}$ , and the parity select  $c_u.ps \in \mathbb{B}^3$ . We omit details here.

The UART has eleven different registers, which are mapped to eight different addresses. Hence, some addresses are used in different contexts. They map to different registers either depending on the access type (read / write operation) or depending on the value of the divisor latch access bit  $c_u.dlab$  (see Table 1).

#### 4.2 Processor-Side Transitions

As already mentioned, the transition function  $\delta_u$  of the serial interface is split into two logical parts: a processor-side and an environment-side transition function.

The processor-side transition function  $\delta_{u}^{\text{mem}}$  defines the behavior of the serial interface when communicating with the processor. Given a current configuration of the serial interface and an input from the processor, it computes an updated serial interface configuration and an output to the processor, i.e.,  $\delta_{u}^{\text{mem}}(c_{u}, mif_{u}) = (mif_{u}, c'_{u})$ .

#### 12 Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev, Sergey Tverdyshev

| UART Register / Buffer            | Por | t Abbreviation | n Access Type            |

|-----------------------------------|-----|----------------|--------------------------|

| Transmitter Holding Buffer        | 0   | $THB_{p}$      | Write, $dlab = 0$        |

| Receiver Buffer                   | 0   | $RB_{\rm p}$   | Read, $dlab = 0$         |

| Divisor Latch Low Byte            | 0   | $DLLB_{p}$     | Read / Write, $dlab = 1$ |

| Interrupt Enable Register         | 1   | $IER_{p}$      | Read / Write             |

| Divisor Latch High Byte           | 1   | $DLHB_{p}$     | Read / Write, $dlab = 1$ |

| Interrupt Identification Register | 2   | $IIR_{\rm p}$  | Read                     |

| FIFO Control Register             | 2   | $FCR_{\rm p}$  | Write                    |

| Line Control Register             | 3   | $LCR_{p}$      | Read / Write             |

| Line Status Register              | 5   | $LSR_{\rm p}$  | Read                     |

|                                   |     |                |                          |

Table 1. Ports of the serial interface

Note that the transition function  $\delta_u^{mem}$  is only partially defined because some processor accesses to the device are considered illegal and lead to an undefined device configuration. Later on we will formulate software conditions excluding all these cases.

In the following we abbreviate a read access to port x by  $rd(mif_i, x) = mif_i.rd \land mif_i.a = x$  and a write access to port x by  $wr(mif_i, x) = mif_i.wr \land mif_i.a = x$ . Although in general we allow devices to have ports of width 32 bit, the serial interface only has ports of width 8 bit. Hence, only the lower 8 bits of  $mif_i.din$  and  $mif_0$  are significant. In the following we assume that  $mif_0$  will be zero-padded by the device and omit these extra bits here.

*Configuration Updates.* If the bit *dlab* is cleared and the processor reads the port receiver buffer having the address  $RB_p$  and the receiver queue of the serial interface is not empty then its first byte is popped. Furthermore the queue maintaining transmission errors for received bytes is updated, too:

$$rd(mifi, RB_{p}) \land c_{u}.dlab = 0 \land c_{u}.rb.len > 0 \implies (c'_{u}.rb = pop(c_{u}.rb)) \land (c'_{u}.trerr = pop(c_{u}.trerr))$$

The processor writes the byte to be transmitted into the port transmitter holding buffer. If the corresponding queue is not full, the written byte is pushed into it:

$wr(mif_{\rm n}, THB_{\rm p}) \wedge c_{\rm u}.thb.len < 16 \implies c'_{\rm u}.thb = push(c_{\rm u}.thb, mif_{\rm n}.din[7:0])$

Pending interrupt flags, raised by the device, are cleared if the processor reads the corresponding ports. Reading the receiver buffer clears the received data availableand the time-out interrupt. Similarly reading the interrupt identification register or reading the transmitter holding buffer clears the transmitter holding buffer empty interrupt. Finally the receiver line status interrupt is cleared by reading the line status register:

$\begin{array}{ll} rd(\textit{mifi}, \textit{RB}_{p}) & \Longrightarrow \ c'_{u}.\textit{rdai} \ = 0 \land c'_{u}.\textit{toi} = 0 \\ rd(\textit{mifi}, \textit{THB}_{p}) \lor \textit{rd}(\textit{mifi}, \textit{IIR}_{p}) & \Longrightarrow \ c'_{u}.\textit{threi} = 0 \\ rd(\textit{mifi}, \textit{LSR}_{p}) & \Longrightarrow \ c'_{u}.\textit{rlsi} \ = 0 \end{array}$

By writing the port interrupt enable register, the programmer can specify which interrupt types are enabled, i.e., which can be raised by the device. Since the timeout interrupt is enabled when the received data available interrupt is, only three bits are relevant. The other five bits are ignored:

$$wr(mifi, IER_{p}) \implies (c'_{u}.erdai = mifi.din[0]) \land (c'_{u}.ethrei = mifi.din[1]) \land (c'_{u}.erlsi = mifi.din[2])$$

The transmit or receive FIFO can be cleared manually by the programmer through writing the FIFO control register  $FCR_p$ . The bit zero of the  $FCR_p$  indicates if FIFOs should be used at all. If it is cleared no buffers will be used.

Setting bits one and two will clear the receiver and transmitter buffers, resp.:

$$wr(mif_{\rm h}, FCR_{\rm p}) \wedge mif_{\rm h}.din[1] = 1 \implies c'_{\rm u}.rb.len = 0 \wedge c'_{\rm u}.rb.hd = c_{\rm u}.rb.tl$$

$$wr(mif_{\rm h}, FCR_{\rm p}) \wedge mif_{\rm h}.din[2] = 1 \implies c'_{\rm u}.tb.len = 0 \wedge c'_{\rm u}.tb.hd = c_{\rm u}.tb.tl$$

Bit three indicates if DMA is supported. In this paper we do not deal with DMA. Bit four and five of the  $FCR_{p}$  are reserved.

If the received data available interrupt is enabled, the last two bits of the  $FCR_{\rm p}$  encode at what length of the receive queue an interrupt is generated. Hence, the two bits map to the *rbitl* component of the serial interface:

$$wr(mifi, FCR_p) \implies c'_{u}.rbitl = mifi.din[7:6]$$

The first two bits of the line control register are mapped to the transmission word length wl, bit two relates to the stop bit length sbl, bits three to five map to the parity select ps, bit seven is set to access the two divisor bytes, and bit six is reserved:

$$wr(mifi, LCR_{p}) \implies (c'_{u}.wl = mifi.din[1:0]) \land (c'_{u}.sbl = mifi.din[2]) \land (c'_{u}.ps = mifi.din[5:3]) \land (c'_{u}.dlab = mifi.din[7])$$

By writing the divisor latch high byte register  $DLHB_p$  and the divisor latch low byte register  $DLLB_p$  the divisor div is set:

$$wr(mifi, DLLB_{p}) \land c_{u}.dlab = 1 \implies c'_{u}.div[7:0] = mifi.din[7:0]$$

$$wr(mifi, DLHB_{p}) \land c_{u}.dlab = 1 \implies c'_{u}.div[15:8] = mifi.din[7:0]$$

*Generated Output.* The predicate  $is_int$  indicates if for a given configuration of the serial interface  $c_u$  at least one of the four interrupts types is pending:

$$is_{int}(c_{u}) = c_{u}.threi \lor c_{u}.rdai \lor c_{u}.rlsi \lor c_{u}.toi$$

In case of a write operation the 32-bit wide data output *mifo* is irrelevant and therefore set to zero. In case of a read operation the first 24 bits of the output are filled with zeros since the serial interface operates byte-wise.

14 Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev, Sergey Tverdyshev

If the processor reads from the receiver buffer and the receive queue is not empty, the first byte is taken from the queue and returned to the processor:

$$rd(mifi, RB_{p}) \land c_{u}.dlab = 0 \land c_{u}.rb.len > 0 \implies$$

$$mifo = head(c_{u}.rb) \land c'_{u}.rb = pop(c_{u}.rb)$$

If the processor reads port  $DLLB_{\rm p}$ , the lower eight bits of the divisor component div are returned. If it reads port  $DLHB_{\rm p}$ , the upper eight bits of the divisor component div are returned:

$$rd(mifi, DLLB_{p}) \land (c_{u}.dlab = 1) \implies mifo = c_{u}.div[7:0]$$

$$rd(mifi, DLHB_{p}) \land (c_{u}.dlab = 1) \implies mifo = c_{u}.div[15:8]$$

When reading the interrupt enable register the output encodes the four flags indicating which interrupt types are enabled:

$$rd(mifi, IER_{p}) \land (c_{u}.dlab = 0) \implies mifo = 0^{5} \circ c_{u}.erlsi \circ c_{u}.erlsi \circ c_{u}.erdai$$

The type of the interrupt that caused the *eev* flag to be set can be checked by reading the interrupt identification register. For  $rd(mif_i, IIR_p)$  we define  $mif_0 = 1100 \circ is \circ \neg is_int(c_u)$  where the three interrupt status bits  $is \in \mathbb{B}^3$  are defined as follows:

$$is = \begin{cases} 011 & \text{if } c_{u}.rlsi \\ 010 & \text{if } \neg c_{u}.rlsi \land (c_{u}.rdai \lor c_{u}.toi) \\ 110 & \text{if } \neg c_{u}.rlsi \land \neg (c_{u}.rdai \lor uart.toi) \\ 001 & \text{if } \neg uart.rlsi \land \neg (uart.rdai \lor uart.toi) \land uart.threi \end{cases}$$

.

The line status register is a read-only register which encodes the polling mode information of the transmitter and the receiver queues. Furthermore, in case of a transmission error (i.e., in case of *line status interrupt*), this register provides the error type. Remember that the component  $c_u$ .trerr stores parity, framing and break errors of all bytes in the receiver queue. When reading  $LSR_p$ , the errors occurred in the head of the queue are reported in bits two, three and four. Let errQ denote whether at least one error occurred in any of the bytes in the queue. Reading the port  $LSR_p$  results in:

$$rd(mif_{i}, LSR_{p}) \implies mif_{0} = errQ \circ c_{u}.edhr \circ c_{u}.ethb \circ head(c_{u}.trerr)[2:0] \circ c_{u}.oe \circ c_{u}.dr$$

The line control register can also be read out. As mentioned before it contains the parity select, word length, stop bit length, set break interrupt enable flag and the divisor latch bit components of the serial interface:

$$rd(mifi, LCR_{p}) \implies mifo = c_{u}.dlab \circ c_{u}.ebi \circ c_{u}.ps \circ c_{u}.sbl \circ c_{u}.wl$$

#### 4.3 Environment-Side Transitions

We describe the interaction of the serial interface with the environment, which is given by the environment-sided transition function  $\delta_u^{env}$ . This function takes an input from the environment and a serial interface configuration and it returns an updated serial interface configuration and an output to the environment, i.e.,  $\delta_u^{env}(c_u, eif_i) = (eif_0, c'_u)$ .

The input from that environment is given by (i) a bit *eifi.tshrready* indicating if the transmitter shift register is empty and hence the next byte of the transmitter queue can be sent, (ii) a bit *eifi.serdinvalid* indicating if new and valid data was received, (iii) the serial input data *eifi.serdin*, (iv) three bits indicating parity, framing, and break error, *eifi.pe*, *eifi.fe* and *eifi.be*, (v) and a bit *eifi.to* indicating a time-out interrupt. Since no time is modeled, a non-deterministic input from the environment signals time-out. The only output of the serial interface to the environment is the byte being sent.

If the transmission shift register is empty *eifi.tshrready* and the transmitter queue has data in it,  $c_u.thb.len > 0$ , the first byte of the queue is sent,  $head(c_u.thb)$  to the external environment. Otherwise, a special empty output is transmitted, i.e.,  $0^8$ .

The byte written to the external environment is taken from the transmitter queue:

$eifi.tshrready \land c_{u}.thb.len > 0 \implies c'_{u}.thb = pop(c_{u}.thb)$

If the receive queue is not full, received bytes are added to it. Furthermore the queue maintaining the parity, framing and break errors is updated for the received byte:

$$eifi.serdinvalid \land c_{u}.rb.len < 16 \implies c'_{u}.rb = push(c_{u}.rb, eifi.serdin) \land c'_{u}.trerr = push(c_{u}.trerr, eifi.pe \circ eifi.fe \circ eifi.be)$$

If a new byte is received although the receive queue is full, then the new byte is dropped and an error is indicated by raising the overrun flag:

$eifi.serdinvalid \wedge c_{u}.rb.len = 16 \implies c'_{u}.oe = 1$

The interrupt pending signals are raised if (i) the transmitter queue is empty and the environment signals through eifi.tshrready that the next byte can be sent,  $c'_{u}.threi = c'_{u}.thbp.len > 0$ , (ii) the length of the receiver queue reaches the specified trigger level (receive data available interrupt),  $c'_{u}.rdai = c_{u}.rb.len \ge itl(c_{u}.rbitl)$ , (iii) or a framing, parity, break or an overrun error occurs (line status interrupt),  $c'_{u}.rlsi = eifi.fe \lor eifi.pe \lor c'_{u}.oe$ , (iv) or the receiver queue is non-empty and the external environment signals the occurrence of a time-out,  $c'_{u}.toi = eifi.to \land c'_{u}.rb.len > 0$ .

In the polling driven mode the configuration is updated similarly: (i)  $c'_{u}.ethb$  is set if the transmitter queue is not empty,  $(c'_{u}.thbp.len = 0)$ , (ii)  $c'_{u}.dr$  is set if the receiver queue is non-empty,  $(c'_{u}.rb.len > 0)$ , (iii)  $c'_{u}.edhr$  is set if both the transmitter queue and the shift register are empty,  $(c'_{u}.thbp.len = 0) \land eifi.tshrready$ . 16 Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev, Sergey Tverdyshev

#### 4.4 Software Conditions and Environment Restrictions

The transition function  $\delta_u$  is not total. Undefined cases are related to over- and underruns of the queues and illegal accesses to unmodeled or write-only ports. Formally, we characterize these cases by predicates over memory input and UART configurations:

- The line-status register must not be written,  $\neg wr(mif_{i}, LSR_{p})$ , and the unmodeled ports  $MCR_{p}$  and  $MSR_{p}$  must not be accessed,  $mif_{i}.a \notin \{MSR_{p}, MCR_{p}\}$ .

- The receiver buffer must not be read when empty and the transmitter buffer must not be written to when full. Formally, if  $c_{\rm u}.dlab = 0$  then  $rd(mif_{\rm u},RB_{\rm p}) \implies c_{\rm u}.rb.len > 0$  and  $wr(mif_{\rm u},THB_{\rm p}) \implies c_{\rm u}.thb.len < 16$ .

Only if these software conditions are met, we can assume the model to be accurate. The driver programmer is responsible for discharging them. For example, a driver which writes no more than 16 byte chunks between each two transmitter holding buffer empty interrupts, obviously fulfills the second condition.

For proving correctness of a driver implementation we need to impose further restrictions on the behavior of the environment.

*Liveness.* We need to assume liveness of the sending part: data in the transmitter buffer must eventually be sent,  $\forall i \exists j > i . seq_{PD}(j) = D_{uart} \land eifiseq(j).tshrready = 1.$

Also the processor is assumed to be live,  $\forall i \exists j > i \cdot seq_{PD}(j) = P$ . While liveness can be assumed by the programmer, it has to be shown in the hardware correctness proof.

*Overrunning Receiver Queue.* The speed of the environment sending packets to the serial interface is not related in any sense to the speed of the processor; packets arrive completely non-deterministically. The question is: how can a driver programmer under these circumstances assure that no packets are lost due to overrunning queues?

This is a tricky task. In a first approach we might impose timing restriction on the environment. Hardware implementation details like caches, pipelining, etc. are invisible in the ISA. Thus, the numbers of instructions executed cannot be related to real time and a relation between transmission speed and ISA execution cannot be established.

Note that the problem of overrunning queues is not inherent to our way of modeling. It is a problem that a device programmer must expect and deal with in nonreal-time operating systems, too. This situation leads to serious difficulties in the formalization of the correctness statements for serial interface drivers. For example, it is impossible to prove that all key presses sent from a keyboard to a serial interface are finally processed by the driver because the model contains runs in which the environment is too fast leading to a queue overrun. There are three approaches to deal with the problem:

| 0:  | addi r3,r0, $\#Da(D_{uart})$                                  | (1.1)  | 44: sw $THB_{ m p}\cdot4({ m r3})$ , r6         | (2.6) |

|-----|---------------------------------------------------------------|--------|-------------------------------------------------|-------|

| 4:  | addi r4,r0,#3                                                 | (1.2)  | 48:slri r6, r6, #8                              | (2.7) |

| 8:  | sw $LCR_{ m p}\cdot4$ (r3),r4                                 | (1.3)  | 52: sw $THB_{ m p}\cdot4$ (r3), r6              | (2.8) |

| 12: | sw $IER_{ m p}\cdot4({ m r3})$ , r0                           | (1.4)  | 56:addi r1, r1, #4                              | (2.9) |

| 16: | addi r0,#14, r4                                               | (1.5)  | $ ightarrow$ 60: 1w r4, $LSR_{ m p}\cdot4$ (r3) | (3.1) |

| 20: | sw $\mathit{FCR}_{\mathrm{p}}\cdot4(\texttt{r3}),\texttt{r4}$ | (1.6)  | 64: andi r4, r4, #32                            | (3.2) |

| 24: | lw r6, 0(r1)                                                  | (2.1)← | 68: beqz r4, #-12                               | (3.3) |

| 28: | sw $THB_{ m p}\cdot 4({ m r3})$ , r6                          | (2.2)  | └-72: nop                                       | (3.4) |

| 32: | slri r6, r6, #8                                               | (2.3)  | 76: subi r5, r5, #1                             | (4.1) |

| 36: | sw $THB_{ m p}\cdot 4({ m r3})$ , r6                          | (2.4)  | 80:bnez r5, #-60                                | (4.2) |

| 40: | slri r6, r6, #8                                               | (2.5)  |                                                 | (4.3) |

Fig. 2. UART driver. We assume that registers r1 and r2 are preset to a and n.

1. *Model overruns in specification and use software synchronization*. A widely used mechanism is called software flow control: the receiver signals the sender when ready / unable to accept new data via the special characters Xon / Xoff.

2. *Hardware synchronization*. Synchronization can also be implemented directly in hardware (called *autoflow control*), as was done for the UART 16750. Using such hardware an assumption can be introduced stating that the environment is not sending new data while the receiver buffer is still full.

3. Worst case execution time (WCET) analysis. Good run-time estimates require a cycle-accurate model for the target processor. Indeed, there are tools for several architectures to precisely estimate the WCET of given programs, e.g., [17]. By analyzing the serial interface driver and parts of the kernel, such as the interrupt handlers, we can compute the latency of processing data received at the serial interface. This yields a maximum baud rate under which the driver may be run safely without overruns.

## 5 Example: A Simple UART Driver

We construct a simple device driver and sketch its correctness proof with respect to the ISA of Sect. 3. The driver writes n words from the processor's memory, starting at address a, to the serial interface with index  $D_{uart}$  and base address  $Da(D_{uart})$ . Its code is shown in Fig. 2; its size is approximately an order of magnitude smaller than the code of a realistic driver for the UART 16550A. We use a MIPS-like syntax. GPRs, immediates, and register-indexed memory operands are denoted as rk, #l, and m(rn). Lines are prefixed with an offset to a certain code base address cba. Arrows indicate jump targets; all jumps are executed with one delay slot.

To state the driver correctness, we use the auxiliary function purge. For a device index idx and an external output sequence eifoseq it returns the sub sequence of external outputs for device idx.

Let  $seq_{PD}$  and *eifiseq* denote a computational sequence and an external input sequence fulfilling the liveness assumption. Let  $c_{PD}^0$  denote an initial configuration which starts with the execution of the driver,  $c_{PD}^0 dpc = cba$ , and where the word

18 Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev, Sergey Tverdyshev

count and start address are stored in the first two registers, i.e.,  $c_{\rm P}^0.gpr[1] = a$  and  $c_{\rm P}^0.gpr[2] = n$ .

Furthermore let  $c_{\text{PD}}^i$  and  $eifoseq^i$  denote the reached state and generated output after the execution  $run_{\text{PD}}(i, seq_{\text{PD}}, eifiseq, c_{\text{PD}}^0)$  of some *i* steps of the combined system.

**Theorem 1** (Functional correctness). There exists some step number e, after which the driver finished execution and the n words from the processor's memory are output to the external environment:  $purge(eifoseq^e, D_{uart}) = c_P^0.m_{4\cdot n}(a)$

*Proof.* The main part of the code is the *outer loop* in parts (2) to (4). It is traversed n times, sending a word over the serial interface in each iteration. Before iteration j < n and after iteration j = n of the loop after a certain number s(j) of steps the following invariants have to hold: (i) j words have been written to the environment,  $purge(eifoseq^{s(j)}, D_{uart}) = c_{P}^{0} \cdot m_{4 \cdot j}(a)$ , (ii) the first address not yet copied and the number of remaining words are stored in gpr[1] and gpr[4], and (iii) the device has an empty transmitter holding buffer, interrupts disabled, and a cleared dlab flag. The existence of s(j) and the invariants are shown by induction over j.

Initially, the device invariant is established by code part (1) writing the ports  $LCR_p$ ,  $IER_p$ , and  $FCR_p$ . For j > 0, correctness of the code that copies a word from memory to the transmitter holding buffer, part (2), and the polling loop, part (3) have to be shown. After part (2),  $4 - c_u \cdot thb \cdot len$  bytes have been transmitted; the other bytes will have been transmitted after the polling loop exits. To show termination of these parts, the liveness condition over the computational and external sequence has to be applied.

#### 6 Conclusion and Future Work

We have presented the detailed formal model of a serial interface controller, the UART 16550A [16]. By combining this model with the formal model of a processor ISA, we obtained a formal model of a processor in which the UART may be accessed as a memory-mapped device. All presented models have been specified in the theorem prover Isabelle/HOL [18]. The formalized ISA resembles the DLX instruction set architecture that was taken as a specification for the VAMP processor [2, 3].

Our Isabelle/HOL formalization defines a precise programming model for device drivers and may be used as the basis of an integrated, self-contained formal driver verification environment. Thus, it is relevant for both device programmers and verification engineers.

For the programmer, the model is a succinct description of the visible state of the device and its interaction with the external environment and the processor. Moreover, *environmental conditions*, which the programmer may assume, and *software conditions*, which the programmer must satisfy, precisely define the rules for implementing

a functionally correct device driver. An example of such a driver, transmitting data via a serial interface, was given in Sect. 5.

In addition, the model may be used by the verification engineer to develop mathematical software correctness proofs and to check them with a computer-aided verification system. A sketch of such a proof was given in Sect. 5. In contrast to related work, the high level of detail in our device models even allows the verification of complex properties like functional correctness rather than just control or protocol properties.

Our further work in this area can be split into two parts. First, we plan to formalize and extend the implementation and correctness proofs from Sect. 5 to cover data reception and successful communication between two serial interfaces. Second, in the broader context of the attempted system verifications in Verisoft, the scope of our modelling and verification effort needs to be extended to cover all system layers from the gate-level hardware of the VAMP processor [2, 3] with devices up to user-level device drivers for a variety of standard devices (e.g., serial interface, hard disk [6], FlexRay-like bus controller). The final result of this effort is a stack of computational models with device support; adjacent layers in this model stack will be related to each other by simulation theorems.

## References

- 1. The Verisoft Consortium: The Verisoft Project. http://www.verisoft.de/(2003)

- Beyer, S., Jacobi, C., Kröning, D., Leinenbach, D., Paul, W.: Instantiating uninterpreted functional units and memory system: Functional verification of the VAMP. In Geist, D., Tronci, E., eds.: CHARME'03. Volume 2860 of LNCS. Springer (2003) 51–65

- Dalinger, I., Hillebrand, M., Paul, W.: On the verification of memory management mechanisms. In Borrione, D., Paul, W., eds.: CHARME'05. Volume 3725 of LNCS. Springer (2005) 301–316

- 4. Schmaltz, J.: A formal model of lower system layer. In: FMCAD'06, IEEE/ACM Press (2006) 191–192

- Knapp, S., Paul, W.: Pervasive verification of distributed real-time systems. In Broy, M., Grünbauer, J., Hoare, T., eds.: Software System Reliability and Security. Volume 9 of IOS Press, NATO Security Through Science Series. (2007) To appear.

- Hillebrand, M., In der Rieden, T., Paul, W.: Dealing with I/O devices in the context of pervasive system verification. In: ICCD '05, IEEE Computer Society (2005) 309–316

- 7. Cohen, B.: Component design by example: A step-by-step process using VHDL with UART as vehicle. VhdlCohen (2000)

- Berry, G., Kishinevsky, M., Singh, S.: System level design and verification using a synchronous language. In: ICCAD, IEEE Computer Society / ACM (2003) 433–440

- 9. ALDEC The Design Verification Company: UART nVS. http://www.aldec.com/products/ ipcores/\_datasheets/nSys/UART\_nVS.pdf (2006)

- 10. Rashinkar, P., Paterson, P., Singh, L.: System-on-a-Chip Verification: Methodology and Techniques. Kluwer Academic Publishers, Norwell, MA, USA (2001)

- Ball, T., Rajamani, S.K.: Automatically validating temporal safety properties of interfaces. In Dwyer, M.B., ed.: SPIN. Volume 2057 of LNCS. Springer (2001) 103–122

- Microsoft Corporation: SDV: Static driver verifier. http://www.microsoft.com/whdc/ devtools/tools/sdv.mspx (2004)

- 13. Hallgren, T., Jones, M.P., Leslie, R., Tolmach, A.P.: A principled approach to operating system construction in Haskell. In Danvy, O., Pierce, B.C., eds.: ICFP, ACM (2005)

- Holzmann, G.J.: New challenges in model checking. http://www.easychair.org/FLoC-06/ holzmann\_25mc\_floc06.pdf (2006) Symposium on 25 years of Model Checking, Seattle, USA. Invited talk.

- 20 Eyad Alkassar, Mark Hillebrand, Steffen Knapp, Rostislav Rusev, Sergey Tverdyshev

- 15. Müller, S., Paul, W.: Computer Architecture: Complexity and Correctness. Springer (2000)

- 16. National Semiconductor: PC16550D universal asynchronous receiver / transmitter with FIFO's. http: //www.national.com/ds.cgi/PC/PC16550D.pdf (2005)

- 17. Ferdinand, C., Heckmann, R.: Verifying timing behavior by abstract interpretation of executable code. In Borrione, D., Paul, W., eds.: CHARME'05. Volume 3725 of LNCS. Springer (2005) 336–339

- 18. Nipkow, T., Paulson, L.C., Wenzel, M.: Isabelle/HOL: A Proof Assistant for Higher-Order Logic. Volume 2283 of LNCS. Springer (2002)

# A Mechanization of Phylogenetic Trees

Mamoun Filali filali@irit.fr

IRIT CNRS Université Paul Sabatier 118 Route de Narnonne F-31062 Toulouse France

**Abstract.** We study the mechanization of phylogenetic trees in higher order logic. After characterizing trees within such a logic, we state how to reason and to compute about them. We introduce the so called generative partitions and relations whose purpose is to allow the reconstruction of a tree from its leaves. After introducing tree transformations, we define the graft operation. and consider sufficient conditions for the preservation of the generative partitions or relations after a graft. It follows that we can reconstruct a tree given its set of leaves and its generative relation which has been preserved along the growth of the tree. We apply this result to the reconstruction of a distributed computation.

keywords: HOL, tree structure, verification, ISAR.

# 1 Introduction

This paper gives a definitional formalization, in higher order logic (HOL), of phylogenetic trees. We also formalize how to reason and compute on such trees. We define the notion of a generative relation, that aims at characterizing information which enables to rebuild a tree. Finally, we propose a reconstruction algorithm based on the set of leaves and a generative relation. The correctness of the algorithm is established. We introduce an operation, the graft, that allows to represent the growth of a tree. a graft are stated. We illustrate such a reconstruction through the so-called leaf vectors and a concrete generative relation. It should be stressed that our study is not only concerned with the proposal of an original algorithm but also by the formal definitions and proofs within a logical framework.

The rest of this paper is organized as follows: Section 2 gives the representation and the basic operations. Section 3 introduces the graft operation and studies its reconstruction properties. Section 4 presents a concrete example where we apply the reconstruction algorithm. Section 5 contains the conclusions and related works.

# 2 A phylogenetic tree representation and basic operations

In this section, we introduce the formal representation of phylogenetic trees; For such a representation, we consider how to reason about it and how to compute on it. We rely mainly on basic set theory. However, rather than working with set theory only, we use type theoretic reasoning also. We have done the mechanization within the Isabelle logical framework [13]. Actually, we have used the Isabelle/Isar<sup>1</sup> [19] environment which goal is to assist in the development of human-readable proof documents composed by the user and checked by the machine.

## 2.1 Notations and basic definitions

In this section, we recall the basic set theory and order notions, we will use.We hope that the name of the definitions and their formal expression are self explanatory. We have used the definitions given in [6]. Moreover, we express them in the Isabelle syntax [13]. For each definition, first, we give its signature, then its formal expression. For instance, we have used the following definitions:

"Maximal  $\triangleq \lambda$  S. {m  $\in$  S.  $\forall$  m'  $\in$  S. m  $\subseteq$  m'  $\Rightarrow$  m = m'}" "Down  $\triangleq \lambda(S, e)$ . {s  $\in$  S. s  $\subseteq$  e}" "PDown  $\triangleq \lambda(S, e)$ . {s  $\in$  S. s  $\subset$  e}" --{\* proper partition\*} "PPartition  $\triangleq \lambda$  (n,S).Partition(n,S)  $\land$  ( $\forall$  e  $\in$  S. e  $\subset$  n)" "A//r  $\triangleq \bigcup x \in A$ . {r''{x}}" --- {\* set of equiv classes \*}

In Isabelle, the reflexive transitive closure of relation  $\mathbf{r}$ , denoted  $\mathbf{r}^* \star$ , is introduced as an inductive data type [2]. Its introduction rules are rtrancl\_refl which specifies that every couple (a,a) belongs to the transitive closure, and rtrancl\_into\_rtrancl which specifies that if (a,b) belongs to  $\mathbf{r}^* \star$  and (b,c) belongs to  $\mathbf{r}$ , then (a,c) belongs also to  $\mathbf{r}^* \star$ .

```

inductive "r^*"

intros

rtrancl_refl : "(a, a) \in r^*"

rtrancl_into_rtrancl :

"(a, b) \in r^* \Longrightarrow (b, c) \in r \Longrightarrow (a, c) \in r^*"

```

With respect to the proofs, we have used the Isabelle/Isar format. A proof is established by a sequence of intermediate results which has to be proved recursively or already established. Eventually, results are justified either as axioms of the logic or by rules of the logic. With respect to proofs, Isar promotes the

<sup>&</sup>lt;sup>1</sup> "Isar" abbreviates "Intelligible semi-automated reasoning".

so called "declarative style" [18] which is closer to the usual mathematical reasoning than the procedural format. Let us mention that, basically, Isar supports natural deduction but also supports calculational reasoning [7].

As an example, the following statement which consists in assumptions<sup>2</sup> (**assumes**), a conclusion (**shows**) and a proof script (**proof**) establishes that the union of two hierarchies (see section 2.2) is also a hierarchy. A basic statement of the proof has the format:

from  $\langle \text{facts} \rangle$  have label ':'  $\langle \text{proposition} \rangle$  by  $\langle \text{method} \rangle$

which aim is to establish proposition from facts by applying method.

```

theorem Hierarchy union:

assumes h1:"H1 ∈ Hierarchy"

assumes h2: "H2 \in Hierarchy"

assumes s: "\forall n1 \in H1. \forall n2 \in H2. SDS(n1, n2)"

shows "(H1 \cup H2) \in Hierarchy"

proof -

from h1 h2 have e: "\emptyset \notin H1 \cup H2" by (unfold

Hierarchy def, blast)

from s have "\forall n1 \in H1. \forall n2 \in H2. SDS(n2, n1)"

by (auto simp only: SDS def)

from this have "\forall n1 \in H2. \forall n2 \in H1. SDS(n1, n2)" by

auto

from s this h1 h2 have sds: "\forall n1 \in H1 \cup H2. \forall n2 \in H1 \cup

H2. SDS(n1, n2)"

by (unfold Hierarchy_def, blast)

from h1 h2 have f: "finite (H1 \cup H2)" by (unfold

Hierarchy def, auto)

from h1 h2 have "\forall n \in H1 \cup H2. finite n" by(unfold

Hierarchy def, auto)

from e sds f this show ?thesis by (unfold Hierarchy def,

blast)

qed

```

#### 2.2 Hierarchies and trees

Our mechanization is based on the introduction of phylogenetic trees starting from the basic notions of set theory. For such a purpose, we first consider hierarchies [3] and then introduce trees as restricted hierarchies. Along with these hierarchies, we give some general definitions that will be used later.

<sup>&</sup>lt;sup>2</sup> Sometimes assumptions are also called preconditions.

24 Mamoun Filali

The basic idea of the following representations is to infer a structure from the relations between its elements; the structure is not encoded directly. Such a content based encoding is motivated by the fact that our basic concern is the reconstruction starting from *some* of the elements, namely the leaves, of the tree structure.

**Hierarchies.** We first introduce a generic graph as a set of nodes. A node is a set of generic elements.

types

```

'e graph = "('e set) set" -- {* generic graph *}

'e node = "('e set)" -- {* generic node *}

```

Hierarchies are finite graphs which elements are finite and non empty and obey to the SDS: "Subset Disjoint Subset" relation:

```

"SDS \triangleq \lambda(s1, s2). s1 \subseteq s2 \lor s1 \cap s2 = \emptyset \lor s2 \subseteq s1"

"Hierarchy \triangleq \{H. \quad \text{finite(H)} \\ \land (\forall n \in H. \quad \text{finite(n)}) \\ \land \emptyset \notin H \\ \land (\forall n1 \in H. \forall n2 \in H. \text{ SDS (n1, n2)}) \\ \}"

```

In the following, we give the formal definitions that will be used.

"Leaves  $\triangleq \lambda$  h.  $\{1 \in h. \text{PDown}(h, 1) = \emptyset\}$ " "ROOT  $\triangleq \lambda$  h.  $\bigcup$  h" "Subtrees  $\triangleq \lambda$  t. image ( $\lambda$  e. Down(t, e)) (Maximal(t))" — {\* proper subtrees \*} "PSubtrees  $\triangleq \lambda$  t. Subtrees (t - Maximal(t))" — {\* roots of proper subtrees, child nodes \*} "R1  $\triangleq \lambda$  t. image ROOT (PSubtrees(t))" "Sigma  $\triangleq \lambda$  S. { $\bigcup$  ( $\bigcup$  S)}  $\cup$  ( $\bigcup$  S)"

Due to the lack of space, we do not state all the established results. We will give them on the fly when needed.

**Trees and phylogenetic trees.** Starting from hierarchies, we first define a tree as a hierarchy with its **ROOT** as the single maximal element :

"Tree  $\triangleq$  {h  $\in$  Hierarchy. Maximal(h) = {ROOT(h)}}"

Then, we introduce phylogenetic trees as trees which nodes are either leaves or the union of all its subnodes:

"Phylo  $\triangleq$ {t \in Tree.  $\forall n \in t. n \in Leaves(t) \lor n = \bigcup PDown(t, n)$ }"

With respect to phylogenetic trees, we just mention the following equality that will allow us to say that the reconstruction can proceed starting from the leaves, while the statement of the reconstruction theorem is over the root. Actually, for a phylogenetic tree t, we have:  $\text{ROOT}(t) = \bigcup \text{Leaves}(t)$ . Moreover, we will rely on the following result about the union of phylogenetic trees:

```

lemma phylo_union:

assumes t1: "t1 ∈ Phylo"

assumes t2: "t2 ∈ Phylo"

assumes u: "ROOT(t2) ∈ Leaves(t1)"

shows "t1 ∪ t2 ∈ Phylo"

proof ... qed

```

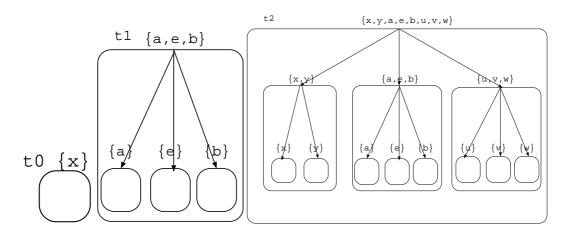

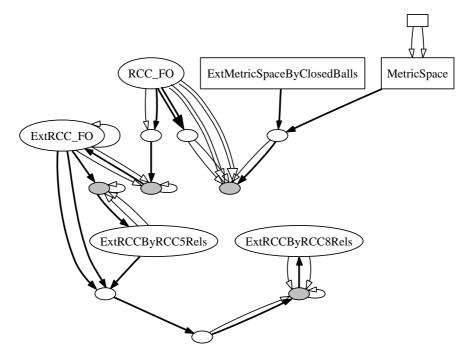

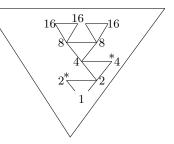

**Examples.** The figure 1 illustrates the representation of phylogenetic trees. For instance, with respect to the previous definitions and the tree let t2, we have:

Fig. 1. phylogenetic trees

26 Mamoun Filali

$$\begin{split} t2 &= \{\{x, y, a, e, b, u, v, w\}, \{x, y\}, \{x\}, \{y\} \\ &, \{a, e, b\}, \{a\}, \{e\}, \{b\}, \{u, v, w\}, \{u\}, \{v\}, \{w\}\} \} \\ \text{Leaves}(t2) &= \{\{x\}, \{y\}, \{a\}, \{e\}, \{b\}, \{u\}, \{v\}, \{w\}\} \} \\ \text{ROOT}(t2) &= \{x, y, a, e, b, u, v, w\} \\ \text{R1}(t2) &= \{\{x, y\}, \{a, e, b\}, \{u, v, w\}\} \end{split}$$

The decomposition and induction theorems. In order to reason about phylogenetic trees, we first introduce a decomposition theorem: a tree is either a singleton containing its ROOT, or the sum (Sigma) of its proper subtrees.

```

theorem phylo_cases:

assumes t: "t ∈ Phylo"

shows "t = {ROOT(t)} ∨ t = Sigma (PSubtrees(t))"

proof ... qed

```

We state the induction theorem about phylogenetic trees as follows:

```

theorem phylo_induct:

assumes b: "\forall e. P({e})"

assumes r: "\forall T \in domSigma. (\forall t \in T. t \in Phylo \land P(t))

\Rightarrow P(Sigma(T))"

shows "\forall t \in Phylo. P(t)"

proof ... qed

```

where domSigma specifies the set of trees which can be "joined" to form a phylogenetic tree:

"domSigma ≜ {S. S ≠ Ø ∧ finite(S) ∧ S ⊆ Tree ∧ (∀ t1 ∈ S. ∀ t2 ∈ S. t1 ≠ t2 ⇒ ⋃ t1 ∩ ⋃ t2 = Ø) ∧ PPartition(⋃ ⋃ S, image ROOT S) }"

# 2.3 Transformations

The basic property of the studied transformations is to preserve the underlying structure while transforming the nodes.

**Hierarchy transformations and preservation theorem.** First, we introduce general transformations which basic property is to preserve the cardinality of a set of nodes.

$"G_tr \triangleq \lambda g. \{tr. \forall n1 \in g. \forall n2 \in g. \\ (tr(n1) = tr(n2)) = (n1 = n2)\}"$

A hierarchy transformation is a general transformation which preserves the relations between the nodes of a hierarchy:

$\{ * \text{ hierarchy transformations set } * \}$   $"H_tr \triangleq \lambda h.$  $<math display="block"> \{ tr \in G_tr(h). (\forall n \in h. \text{ finite}(n) \Rightarrow \text{ finite}(tr(n)))$  $\land (\forall n \in h. n \neq \emptyset \Rightarrow tr(n) \neq \emptyset)$  $\land (\forall n1 \in h. \forall n2 \in h. n1 \subseteq n2 \Rightarrow tr(n1) \subseteq tr(n2))$  $\land (\forall n1 \in h. \forall n2 \in h. n1 \cap n2 = \emptyset \Rightarrow tr(n1) \cap tr(n2) = \emptyset)$  $}"$

A hierarchy is preserved by a hierarchy transformation:

```

theorem hierarchy_trans:

assumes t: "t ∈ Hierarchy"

assumes tr: "tr ∈ H_tr(t)"

shows "image tr t ∈ Hierarchy"

proof ... qed

```

A tree is also preserved by a hierarchy transformation.

**Phylogenetic transformations and preservation theorem.** Intuitively, when a phylogenetic transformation is applied to a non-leaf node, the decomposition into its descendant nodes is preserved. The characterizing property of a phylogenetic transformation is expressed as follows:

$"P_tr \triangleq \lambda h. \{ tr \in H_tr(h). \forall n \in h. \\ n \in Leaves(h) \lor tr(n) = \bigcup (image tr (R1(Down(h,n)))) \}"$

Then, we state the preservation theorem:

```

theorem phylo_trans:

assumes t: "t ∈ Phylo"

assumes tr: "tr ∈ P_tr(t)"

shows "image tr t ∈ Phylo"

proof ... qed

```

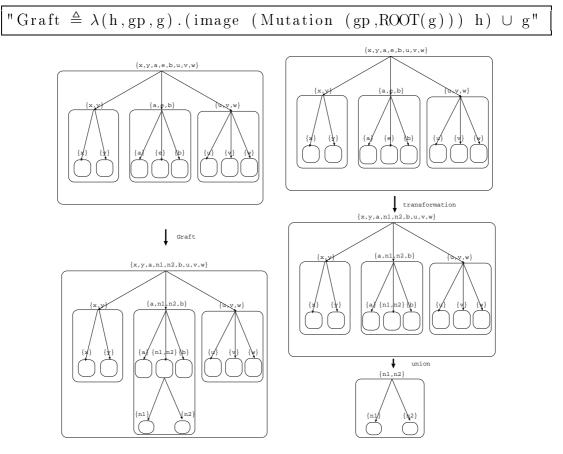

**Example.** A Mutation is a transformation that concerns the nodes up a graph node: gp, such "up" nodes contain gp, and a mutation is expressed as follows:

"Mutation  $\triangleq \lambda(gp,R) . \lambda$  n. if  $gp \subseteq n$  then  $(n - gp) \cup R$  else n"

We show that the Mutation transformation is a phylogenetic transformation:

```

theorem Mutation_P_tr:

assumes h: "h ∈ Phylo"

assumes g: "g ∈ Phylo"

```

28 Mamoun Filali

```

assumes pre: "PreGraft(h,gp,g)"

shows "Mutation(gp,ROOT(g)) ∈ P_tr(h)"

proof ... qed

```

where **PreGraft** (We will use this predicate as the precondition of the **Graft** operation.) is defined as follows:

```

"PreGraft \triangleq \lambda(h, gp, g). h \in \text{Hierarchy} \land (((\text{ROOT } h) \cap (\text{ROOT } g)) = \emptyset) \land

gp \in \text{Leaves}(h) \land g \in \text{Hierarchy} \land g \neq \emptyset"

```

# 2.4 Generative partitions and relations